| ID |

Date |

Author |

Type |

Category |

Subject |

|

582

|

Mon May 26 23:24:33 2025 |

Michael | Update | Interferometer Simulations | Initial Monte Carlo Simulations for Toroidal Mirrors Project |

| I've run an initial Monte Carlo simulation for statistical comparison of toroidal mirrors for the dual FROSTI TCS case. Below is the link to the slides.

slideshow |

|

571

|

Tue May 6 13:07:34 2025 |

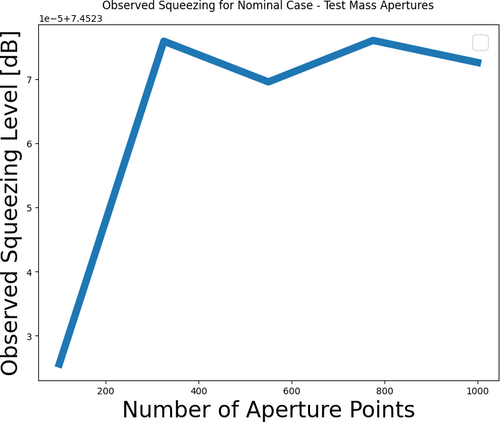

Michael | Update | Interferometer Simulations | Initial Convergence Plots for Toroidal Mirrors Project |

|

| Attachment 1: Convergence_Plots_5_6_25.pdf

|

|

| Attachment 2: Convergence_Plots_5_6_25-1.pdf

|

|

| Attachment 3: aperture_num_points_convergence.png

|

|

|

373

|

Mon Jun 3 14:14:39 2024 |

Tyler | Update | FLIR | Initial CIT FROSTI Analysis |

| [Tyler]

Attached below are the initial results of the CIT FROSTI testing analysis.

|

| Attachment 1: CIT_FROSTI_Analysis_Group_Meeting-2.pdf

|

|

|

323

|

Tue Feb 13 11:54:45 2024 |

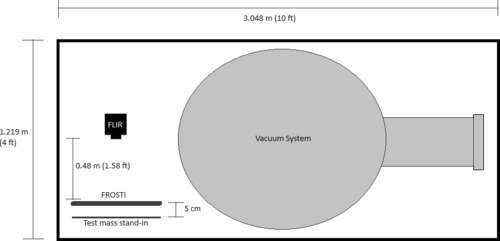

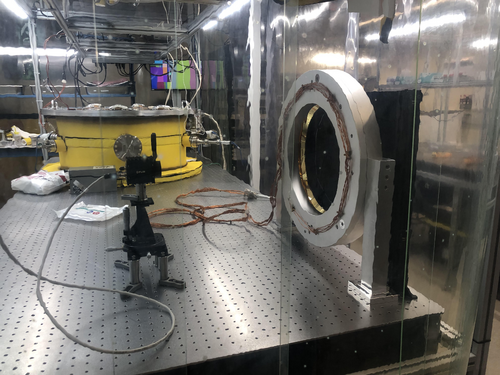

Tyler | Configuration | FLIR | In-Air Optical Test Configuration |

Below is the proposed schematic for FROSTI optical testing, chosen so enough space is allotted for prototype assembly.

Steps to be taken include:

- Reconstruct FLIR staging apparatus

- Move test mass stand-in to cleanroom

- Mark FLIR camera position on cleanroom optical table at correct distance

- Run ethernet cable into cleanroom

- Move FLIR aside to allow for more assembly space

- Upon assembly completion, reposition FLIR onto optical table again

Tentative plan is to begin setup early next week. |

| Attachment 1: In-air_optical_test_sketch.png

|

|

|

349

|

Tue Mar 19 10:55:30 2024 |

Tyler | Update | FLIR | In-Air Optical Test |

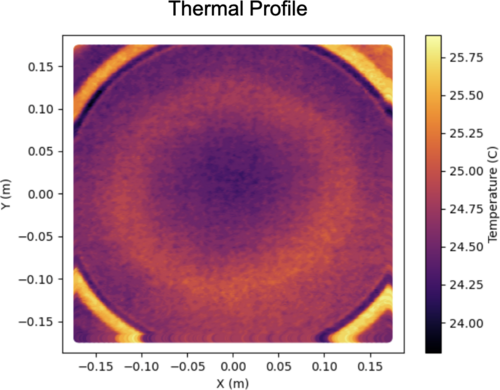

| Below is an image I took using the FLIR just before leaving for the LVK meeting. The profile is roughly what we would expect (annular). Any distortions seen are likely from the screen not being completely parallel to the plane of the FroSTI (i.e. the screen slightly bends in various locations). Next step: In-vacuum test at CIT. |

| Attachment 1: FroSTI_Thermal_Profile.png

|

|

|

468

|

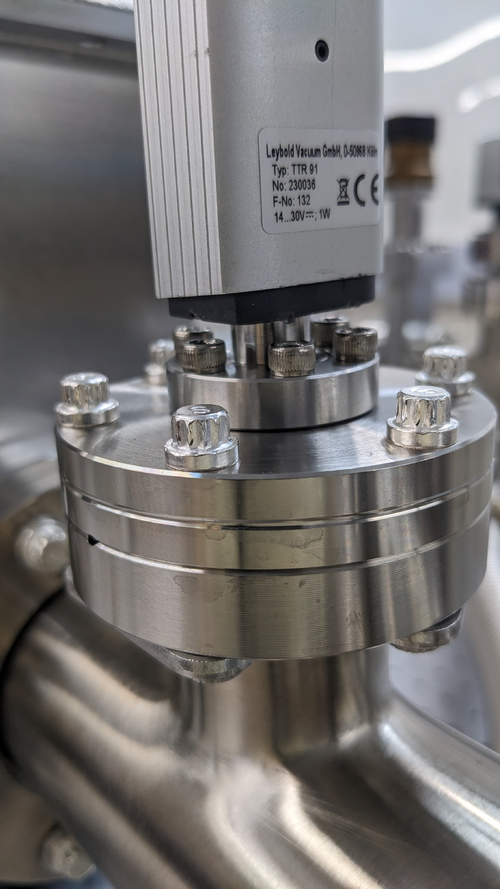

Tue Nov 5 11:08:40 2024 |

Luis Martin | Update | VAC | ISO Test |

|

[Luis, Luke, Ma Michael]

The isolation test was conducted on the vacuum system. Every pump was turned off under vacuum, and pressure measurements were taken every minute for 15 minutes. The results are displayed in the sheet linked at the end of this report. The pressure of the main volume dropped very slowly.

The pressure of the RGA Volume dropped in an exponential manner. The test had to be paused at 11 minutes due to concerns about the pressure exceeding the lowest permitted level for the RGA filament.

After the ISO test was performed, we attempted to tighten the bolts of the small turbo pump on the RGA Volume. However, we noticed that the pressure had increased by nearly an order of magnitude, going from 3.27 � 10-9 Torr to 1.45 � 10-8 Torr when both volumes were separated. We conducted a leak test for that particular flange and found a concerning leak of 2.15 � 10-8 Torr, which had previously been 1.9 � 10-9 Torr. We believe the copper seal was damaged during the ISO test.

View the results sheet

|

|

6

|

Tue Jun 21 18:31:49 2022 |

Cassidy and Phoebe | Update | Cameras | IR Absorbing Screen and FLIR Camera Setup |

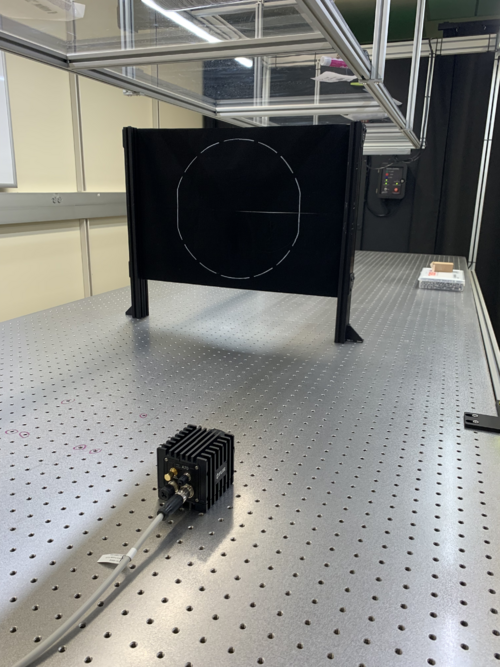

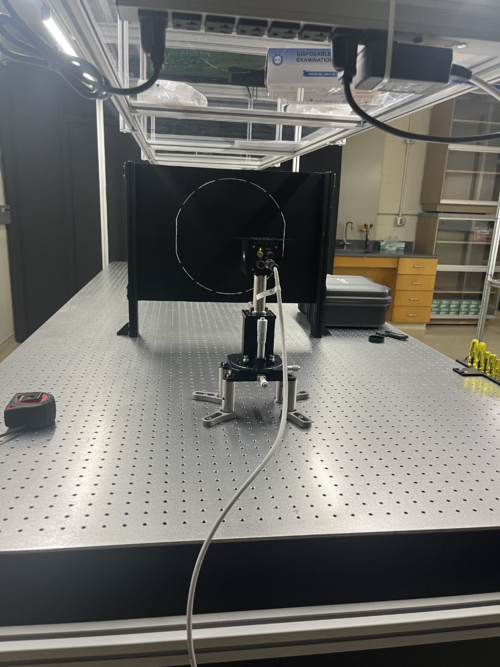

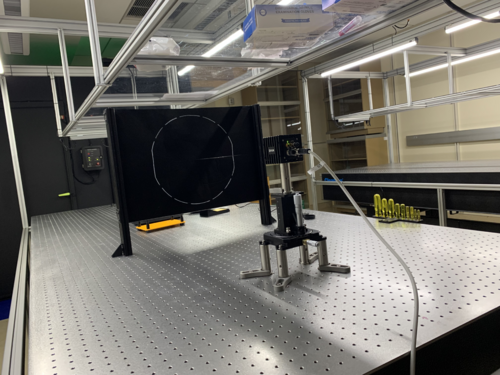

Today we set up the IR absorbing screen and the camera on the optical table, as well as tested that the camera was functioning as expected (picking up heat sources beyond the screen).

Screen Setup

The screen was set up by clamping it between two rectangular posts on each side. First, two posts were set up with 22 in. between them (thus allowing the screen to span a total distance of up to 24 in. when clamped down). To best stabilize the screen and to allow for it to be "pulled" taut by exploiting the give in the L-bracket, the L-bracket was bolted on the outside of the post, along the same axis as the screen itself.

On first attempt, the screen was too thin to be fully clamped between the posts. In order to have it fit snugly, sections of heat shrink tubing was used as a shim at the points where the posts were clamped together. The tubing was slid into the track of one optical post at the desired points. In order to accommodate the shim, the two posts had to be held together, ideally clamped, with the screen and shim in place. Then, the post clamps could be slid into the tracks of the post, moved to the optimal location, and tightened down. This required at least three people: two to tighten one side while the third holds up the screen on the other side. The screen was placed ~1/8" from the edge of the posts and flush with the top.

Camera Stage Setup

Once the screen was in place, the camera stage was set up by placing the XY-Translational with Rotation stage on four 3" optical posts. Then, the z-axis stage was placed in the center of that, with another 3" optical post on top, which was then topped with the camera. This was set and clamped down ~22.5" from the screen. This was about 1" closer than expected based on our theoretical models.

Fine Alignment

We used the visible camera to fine align the screen and to test the setup. Notably, the visible camera is placed below the infrared and thus requires a calibration in order to ensure the two are aligned on the computer image. This can be set by hand using the FLIR proprietary software (FLIR CamWeb) and adjusting the "MSX alignment". The image mode "Thermal MSX" allows both the visible and IR camera to be displayed at once and the difference in their positioning can be seen. We found an offset of ~0.5m to be nearly accurate (note: using this method, although you can get more accurate than this, the displayed value only has one significant figure).

In order to align the camera, we first used the exposed top edge to judge whether the camera was appropriately centered on the screen. We set the rotation as close as possible to being in line by eye, then adjusted the y-axis until the gap on both corners was a similar size, thus indicating that the rotation and y-position were correctly set. Rotationally, the camera required only a refinement of -1/2 degree. The y-axis is set at 1.25. Then, the camera was pulled as far from the screen as possible using the x-axis to allow the screen to be easily centered using the z-axis. Once the outlined test mass was centered, the x-axis was used to bring the camera close until the screen just barely filled the field of view. The x-axis is at 2.25. The z axis is set to it full dynamic range at 10. Unfortunately, the camera is still slightly too tall for the screen, likely requiring the purchase of a new optical post about 0.5in shorter the current one. This interchange will likely require a new fine alignment after.

Basic Imaging Tests

The camera was also focused on the screen based on the manufacturer's printed distance on the camera itself (using 22.5", or 0.572 m). Using the FLIR proprietary software, the camera appears to be in focus in IR (a hand was used as a good focusing tool for this). Additionally, the camera does pick up heat on the other side of the screen. A hand can be lightly seen warming the screen, as can a soldering iron tip. This was a very imprecise visual tool, but does indicate that the camera and screen are working roughly as expected.

Next Steps

A new optical post that is ~2.5" tall should be ordered to replace the one under the camera currently. The heating system also needs to be ordered and set up. Currently we are debating between a parabolic reflector with a hole in the back, and one without, as each would require a different mounting mechanism for the cartridge heater. |

| Attachment 1: IMG_6751.png

|

|

| Attachment 2: IMG_1146.png

|

|

| Attachment 3: IMG_6756.png

|

|

|

60

|

Mon Apr 3 17:04:05 2023 |

Aiden | Summary | General | IDP Scroll Pump Assembly |

| Aiden installed the isolation valve and the exhaust silencer kits on the IDP-3 Scroll pump. The entire assembly still needs to be wiped down but overall no residue came off when putting on the kits. |

| Attachment 1: IMG_4244.jpg

|

|

|

1

|

Sun Apr 10 15:39:49 2022 |

Rutuja Gurav | HowTo | Computer Scripts/Programs | HowTo: Renew the Let's Encrypt SSL certificate using certbot |

Port 80 is kept closed by default. This might be causing the certbot auto-renewal cronjob to fail. Therefore we must renew the certificate manually.

Step 1: Open port 80. (This is needed as the certificate renewal process runs some tests which requires client communication over port 80)

Step 2: Run the following command

sudo certbot certonly --force-renew -d richardsonlab.ucr.edu

Step 3: Confirm the certificate was renewed by running the following command

sudo certbot certificates

|

|

98

|

Sun May 14 15:50:48 2023 |

Cao | Infrastructure | Computers | High resolution display of logrus machine |

| [Cao]

The display resolution of the logrus has been 1064x768 and has been the only option, which is not great. While remote access to logrus using rdesktop allows rendering a virtual display of user's chosen resolution, it is not fast when using graphic-intensive program. NoMachine allows user to take over and control the machine remotely and thus appears as the same machine. However, NoMachine cannot render a virtual display like rdesktop. This has been limiting the resolution of using logrus via NoMachine.

On Friday, I found that even though we had NVIDIA Quadro P600 graphic card installed, we were not actually using it. The monitor has been connecting to the the integrated VGA display connector. This uses Microsoft Basic Display Adapter which limits the the resolution. Today I got a HDMI to Mini-display cable to connector the monitor to the Nvidia graphic card. Then in Display settings, go to Graphic settings, then enable Hardware-accelerated GPU scheduling. After restarting the machine, the machine recognised the Display 2using the Nvidia Quadro P600. In multiple displays field, selected "Show only on 2" and remove the VGA connection to the monitor. Logrus is now set at Nvidia Qadro P600 native display resolution of 1920x1080. This is now also the display resolution in NoMachine.

|

|

543

|

Mon Mar 31 11:26:45 2025 |

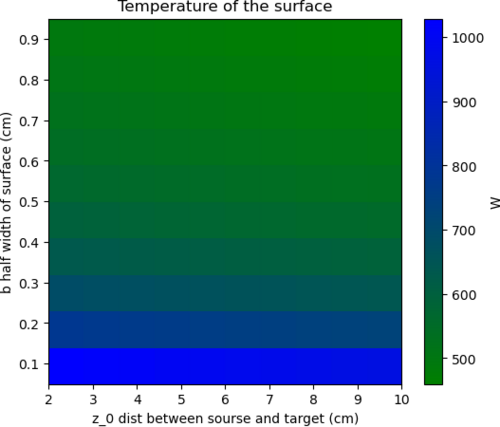

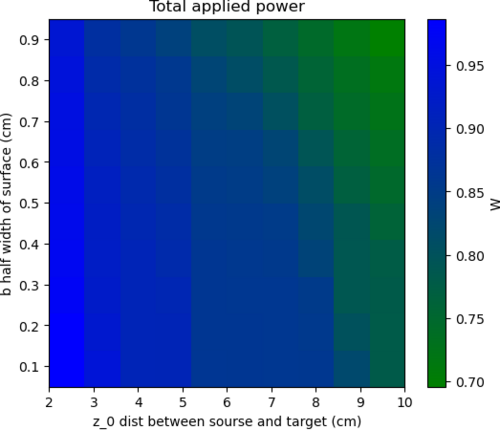

Luke Johnson | Update | Scripts/Programs | Heatmaps of power delivery performance |

| These plots show the required temperature to release 100W of power and the efficiency of a particular configuration with half-width w and distance away from the barrel z. I want to add to these heat maps a limit line that has restricts the proximity of the reflectors from the barrel. |

| Attachment 1: temp_required.png

|

|

| Attachment 2: efficiency.png

|

|

|

435

|

Fri Sep 6 14:34:52 2024 |

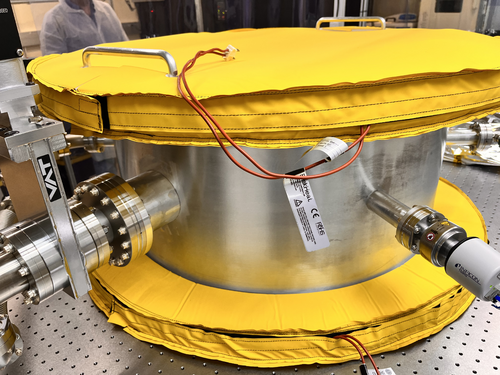

Luke | Update | VAC | Heating tape work |

On the 5th I had tried to start baking the vacuum chamber however certain parts of the chamber were getting too hot and causing the controllers to shut off. So I turned them off so that the next day I could rearrange the temperature probes. I then on the 6th set them up so that instead of overshooting the temperature they would be a little low in places.

After being left over night the cooler parts of the vacuum chamber got much closer to the desired temperature of 120C.

Here is a table of the temperatures of the sections of the chamber. Note: After these measurements were taken the PID controllers were set to 125C.

| Location |

Temperature (C) |

| Lid (PID controller 1 emergency shutoff) |

108 |

| Barrel lower (PID controller 1) |

120 |

| Barrel upper (PID controller 2 emergency shutoff) |

118 |

| RGA volume (PID controller 2) |

120 |

Here is a table of temperature of the flanges that have electronics.

| Electronics |

Temperature (C) |

| Pressure gauge (Main volume) |

79 |

| Main turbo pump |

64 |

| RGA |

51 |

| Pressure gauge (RGA volume) |

55 |

| Cal leak |

47 |

| Mini turbo pump |

50 |

| Pirani gauge |

45 |

Other temperatures of note:

The optical table was about 38C

The cleanroom was around 33C (~91F) |

|

124

|

Wed Jun 14 15:35:36 2023 |

Pamella | Update | VAC | Heating system installation |

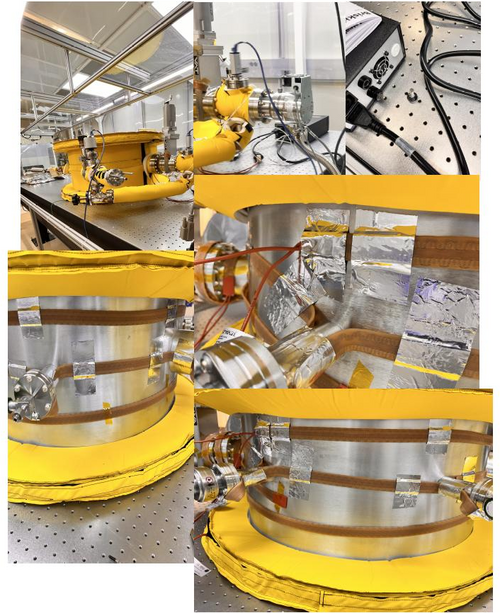

[Pamella and Cao]

Heating system installation - Second day.

- Today we kept installing the equipment for the heating system.

- First: Started installing the two heating cable around the chamber vacuum, the arms and covered it with aluminum tape.

- Second: Started installing the insulation stuff around the vacuum chamber and around the connections points (the arms) in the vacuum chamber.

- Third:Started installing the heater system (electronic device) and tried testing.

-

Note: The around part of the chamber vacuum was difficult to cover, so we spent a little time on. Also one heater system electronic device wasn't working because one fuse is burned so we could not finished this part and we need wait for a new one to replace and working on it.

|

| Attachment 1: heater_equipment_install.jpg

|

|

|

433

|

Tue Sep 3 15:52:56 2024 |

Luke | Update | VAC | Heater tape initilization |

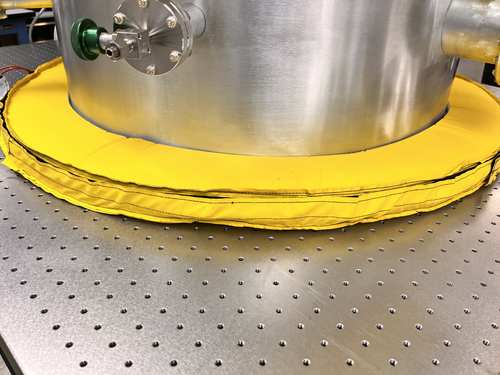

[Luke, Tyler, Jon]

On the 3rd we set up the pid controllers for the heater tapes and after putting on the insulation we started heating them up. We first brought it to ~50C and let it stabilize, there was about a 6-7 degree difference between the RGA and the barrel temperature, with the barrel being higher. We then brought it to 60 then 70C it still maintained the slight difference between the RGA and barrel temperatures.

Here is a table of the temperatures of the flanges connected to electronics as I left it.

| Electronics |

Temperature (C) |

| Pressure gauge (Main volume) |

58 |

| Main turbo pump |

45 |

| RGA |

37 |

| Pressure gauge (RGA volume) |

39 |

| Cal leak |

40 |

| Mini tubo pump |

36 |

| Pirani gauge |

37 |

Notes: I removed the electronics from the pressure gauge (main volume) because while it was below the required threshold it was still quite high compared to the other flanges. |

|

119

|

Mon Jun 12 18:52:00 2023 |

Pamella | Update | General | Heater system parts - Wiped and bagged |

[Pamella]

Cleaning the heater system parts.

- 04:32 pm: Started wiping the heater system parts.

- 06:38 pm: Finished wiping the heater and some parts to the system. I wiped, tagged and bagged the heater system, power cables, adapter cables and power connectors. Also I wiped, bagged and tagged the aluminum foil tape.

- 06:43 pm: I putted all bags inside the cleanroom.

- To do: I started but I was not able to finished wiping the heating and cords for the heater system so I will finished this parts after.

- I attached the photos below.

|

| Attachment 1: heater_equipment_wiped.jpg

|

|

|

128

|

Tue Jun 20 17:28:23 2023 |

Pamella | Update | Electronics | Heater system parts - Wiped |

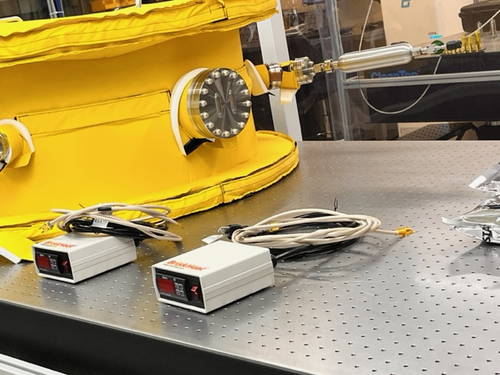

[Pamella]

Wiping the heater system parts.

- 04:37 pm: Started wiping the electronic device part for the heater system (HL101 Series Digital Benchtop temperature limit control).

- 05:19 pm: Finished wiping the parts to the heater system (HL101 Series Digital Benchtop temperature limit control). I wiped the HL101 Series Digital Benchtop temperature limit control and I didn't bagged and tagged because we should install that soon.

- 05:23 pm: I putted heater electronic device inside the cleanroom without the bag. Also the electronic device is near to the vacuum chamber and the other parts to heater system.

- I attached the photo below.

|

| Attachment 1: IMG_7696.jpg

|

|

|

122

|

Tue Jun 13 21:08:46 2023 |

Pamella | Infrastructure | VAC | Heater system - Installation |

[Pamella, Cao and Jon]

Heating system installation

- Today we started installing the equipments for the heating system.

- First: Started installing the heating cable on the top lid and covered it with aluminum tape.

- Second: Started installing the insulation cover on top of the chamber lid.

- Third:Started installing the heating cable from under the vacuum chamber and covered with aluminum tape.

- Forth: Started installing the insulation cover under the vacuum chamber

- Note: The under part of the chamber vacuum was very difficult to cover, so we spent a little time on it and we couldn't finish the whole installation today. So tomorrow we should be able to keep doing the installation.

|

| Attachment 1: IMG_7563.jpeg

|

|

| Attachment 2: IMG_7561.jpeg

|

|

|

503

|

Mon Jan 27 11:29:38 2025 |

Xuesi Ma | Update | | Heater Element Test |

[Ma, Cece, Luke, Mary, Shane]

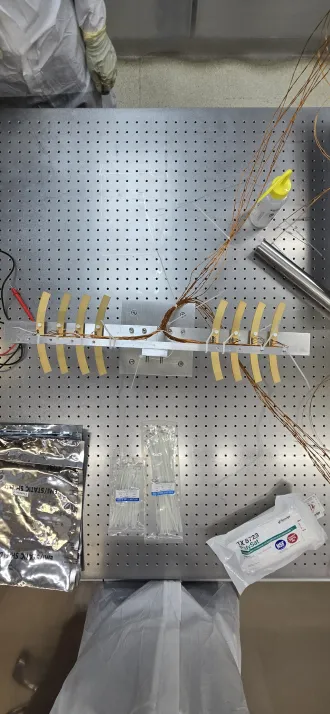

On Friday (Jan 24), we installed the heater elements on the stand. The heater elements are arranged from 1 to 8, oriented from right to left as shown in Attachment 1. Each wire has been labeled according to its corresponding element number and type (e.g., RTD connections, heater connections).

Note: We currently do not have enough PEEK zip ties, so standard zip ties have been used temporarily. These must be replaced with PEEK zip ties before the setup is placed in the vacuum chamber. |

| Attachment 1: 20250124_165434.png

|

|

| Attachment 2: 20250124_165342.png

|

|

| Attachment 3: 20250214_132811.jpg

|

|

|

316

|

Mon Feb 5 14:17:52 2024 |

Aiden | Update | VAC | Heater Element RGA Scan |

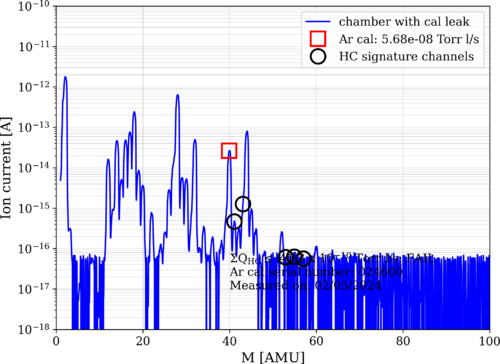

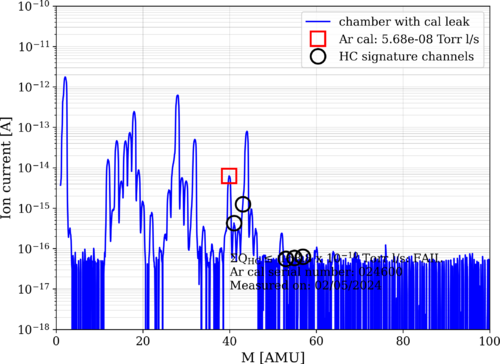

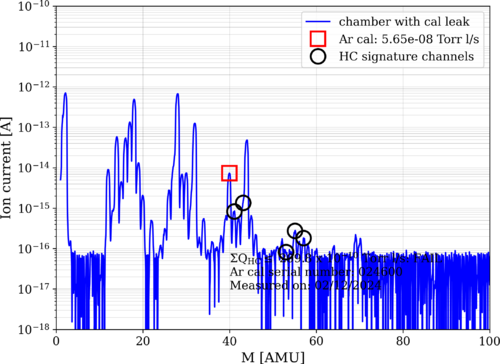

| Here are the new RGA scans for the powered Heater elements. The pressure at the time of taking data was 2.88 e-8 torr. The HC levels are at 40 e-10 torrl/s which is not bad but still higher than the lowest we have recorded. |

| Attachment 1: bake10_240205_Elements_ArO.png

|

|

| Attachment 2: bake10_240205_Elements_ArC.png

|

|

|

319

|

Thu Feb 8 17:37:48 2024 |

Aiden | Update | VAC | Heater Element RGA Scan |

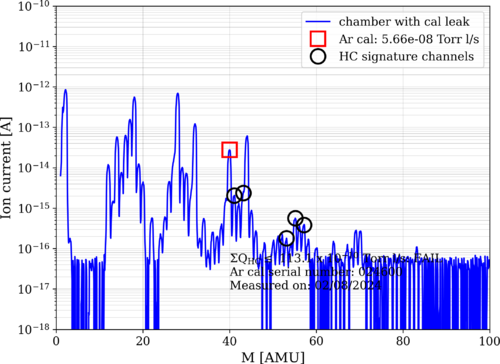

| Took more RGA data now that the heaters are powered by 18V. The pressure of the system during the data taking was 3.8 e-8 torr. The RGA scans seem to have gotten worse as well with this power increase. |

| Attachment 1: bake10_240208_Elements_ArO.png

|

|

| Attachment 2: bake10_240208_Elements_ArC.png

|

|

|

320

|

Mon Feb 12 17:35:47 2024 |

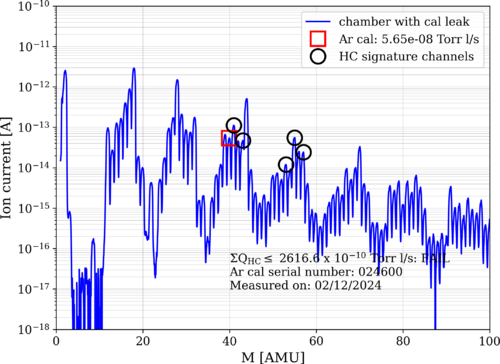

Aiden | Update | VAC | Heater Element RGA Scan |

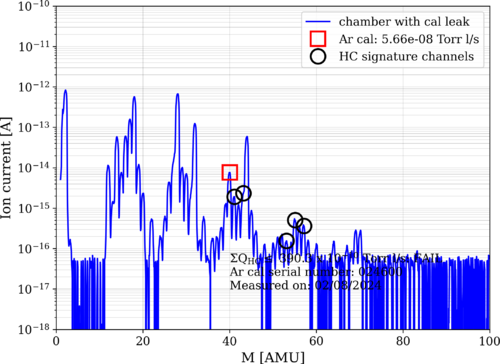

| Took more RGA data before and after increasing the heater elements to 300 degC and before heating them up.

Started Bake 11 as well to hopefully prevent any hydrocarbons from getting captured by the room temperature walls of the chamber. The PID controllers were set to 100C. |

| Attachment 1: bake10_240212_Elements_ArO.png

|

|

| Attachment 2: bake10_240212_Elements_ArC.png

|

|

| Attachment 3: bake10_240212_Elements_300C_ArC.png

|

|

|

328

|

Mon Feb 19 14:17:50 2024 |

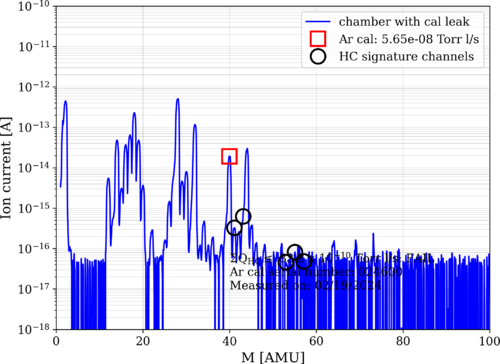

Aiden | Update | VAC | Heater Element RGA Scan |

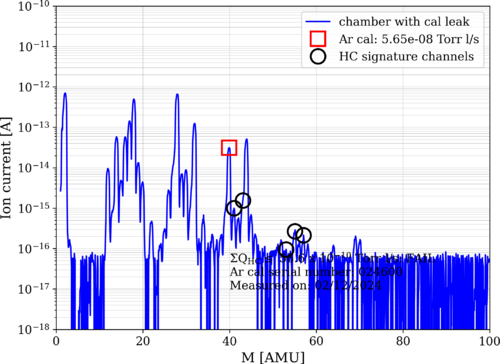

| Three days after the completion of Bake 11, the Heater elements RGA scan looks much cleaner. The HC level is back down to 33 e-10 torrl/s with the pressure at 2.13 e-8 torr. I could not take a= scan with the Argon closed as it was left open during the bake and not closed since then. |

| Attachment 1: bake11_240219_Elements_ArO.png

|

|

|

506

|

Fri Jan 31 15:03:09 2025 |

Xuesi Ma | Update | | Heater Element Circuit Check |

|

[Ma] Wed 1/29/2025

No short circuit between heater element ✓

No short circuit to ground on any pin ✓

No short circuit between connectors ✓

| Heater Number |

Power Resistor before (Ohm) |

Power Resistor now (Ohm) |

RTD Resistor before (Ohm) |

RTD Resistor now (Ohm) |

| 1 |

73.6 |

73.1 |

81.8 |

81.3 |

| 2 |

70.4 |

69.6 |

82.1 |

81.6 |

| 3 |

71 |

70.5 |

84.5 |

84 |

| 4 |

71.5 |

71 |

80 |

79.4 |

| 5 |

70.5 |

70.2 |

81.7 |

81.2 |

| 6 |

72 |

71.6 |

79.4 |

78.7 |

| 7 |

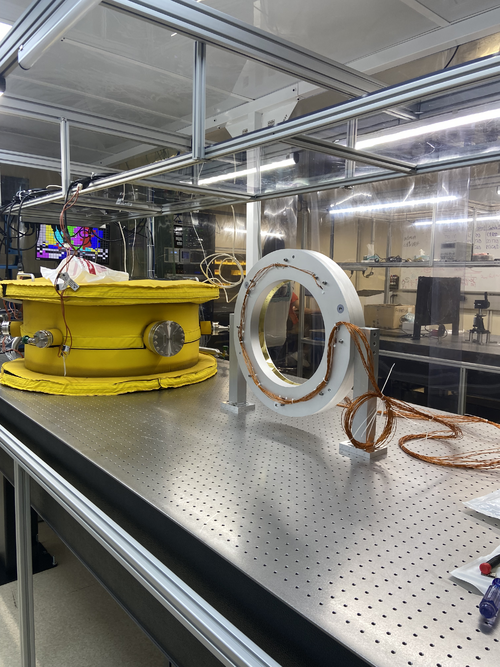

69.2 |

69 |

78.2 |

77.5 |

| 8 |

71.1 |

70.6 |

84.2 |

83.6 |

|

|

609

|

Mon Jul 14 20:45:20 2025 |

Luke | Summary | Cleanroom | HEPA filter performance metrics |

[Luke, Luis]

We’ve been looking into methods for evaluating the performance of the HEPA filters in the clean room. Measuring flow rate appears to be a promising approach, since the filter manual specifies a recommended minimum of 70 ft/min.

At the moment, we don’t have a flow rate measurement device on hand. We're currently looking into two options:

- A standard vane-style anemometer, which is more affordable but may lack sensitivity near the minimum required flow rate.

- A hot-wire anemometer, which offers better resolution and accuracy at lower speeds, though it's more expensive.

In the next few days, either Luis or I will contact Terra Universal to see if they have any measurement solutions that would integrate well with our clean room setup, or if they can recommend best practices for verifying HEPA performance. |

|

7

|

Mon Jul 11 14:29:45 2022 |

Jon | Omnistructure | General | HEPA filter installed |

| Today I unpacked and installed the new HEPA filter for the lab. It is an Omni CleanAir OCA1210 capable of 1200 CFM. This flow rate is sufficient to turn over the air in the room once every 4 minutes, or 14 times per hour. Hopefully this will cut down on our particulate accumulation issues. |

| Attachment 1: IMG_1530.png

|

|

|

701

|

Sun Apr 19 15:22:08 2026 |

Pooyan | Infrastructure | Cleanroom | HEPA fan air flow measurment |

[Ma, Mary, Tyler, Pooyan]

HEPA fan air flow measurements are done with the fans sitting on their side in the lab, and the anemometer being 24in away from the filter face of the fan. Per company's documents, we need to replace the filter if the air flow velocity drops under 38-45 fpm for the medium settings.)

| S/N |

Min |

Avg |

Max |

| P188642-2 |

118 |

121 |

125 |

| 118 |

119 |

125 |

| P188642-3 |

53 |

79 |

88 |

| 43 |

48 |

53 |

| P188642-12 |

43 |

61 |

88 |

| 15 |

42 |

53 |

| P188642-1 |

80 |

83 |

88 |

| 43 |

49 |

80 |

All numbers are in fpm unit. The measurement for each unit is done twice in front of the fan positions. |

|

515

|

Tue Feb 18 10:02:16 2025 |

Xuesi Ma | Update | | Group Meeting Slides 2/18/2025 |

https://docs.google.com/presentation/d/1WiV2VqS0BzXNCK6VYYQ-Ty8xlHnzXatQaFbMf1-0rsY/edit?usp=sharing |

|

451

|

Wed Oct 2 10:31:46 2024 |

Xuesi Ma | Configuration | | Group Meeting Slides 10/2/2024 |

Group Meeting slides for Non-deterministic Heater Response.

|

| Attachment 1: Group_Meeting_10_2.pdf

|

|

|

82

|

Thu Apr 27 21:43:07 2023 |

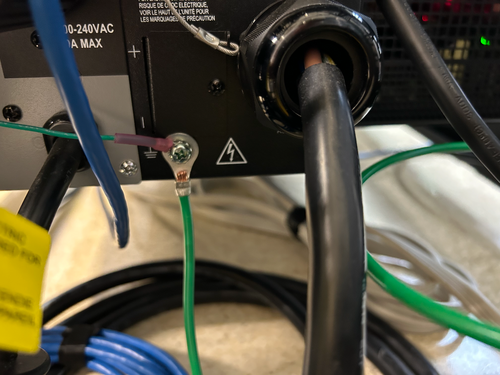

Jon | Physics | VAC | Grounding vacuum system |

This afternoon I made up a green 10 AWG grounding cable and connected it to the vacuum system.

One end is tightly connected to the bottom flange of the vacuum chamber (photo 1). It is run along and up the table framing to the top of the cleanroom, where it exits into the overhead cable tray in the same location as the other power cables. It drops down from the top of the server rack all the way to the bottom, where the other end is connected to the lab's electrical ground in the rear of the 240 V UPS (photo 2).

The connections were confirmed to be secure, but continuity testing with an ohmmeter remains to be done to confirm that the chamber and tabletop are indeed grounded. |

| Attachment 1: IMG_0141.png

|

|

| Attachment 2: IMG_0140.png

|

|

|

84

|

Fri Apr 28 18:16:57 2023 |

Cao | Physics | VAC | Grounding vacuum system |

| Quote: |

This afternoon I made up a green 10 AWG grounding cable and connected it to the vacuum system.

One end is tightly connected to the bottom flange of the vacuum chamber (photo 1). It is run along and up the table framing to the top of the cleanroom, where it exits into the overhead cable tray in the same location as the other power cables. It drops down from the top of the server rack all the way to the bottom, where the other end is connected to the lab's electrical ground in the rear of the 240 V UPS (photo 2).

The connections were confirmed to be secure, but continuity testing with an ohmmeter remains to be done to confirm that the chamber and tabletop are indeed grounded. |

�

[Cao]

Continuity Test

Following from Jon's grounding work on the vacuum system, I did a continuity test with the afternoon with a multimeter. The chamber is indeed grounded:

- Chamber wall to optical table: continuity confirmed, resistance: 0 Ohm

- Chamber wall to ground point connection on chamber: continuity confirmed, resistance: 0 Ohm

- Turbo pump to ground point connection on chamber: continuity confirmed, resistance: 0 Ohm

- Turbo pump to optical table: continuity confirmed, resistance: 0 Ohm

- Optical table to chassis frame outside cleanroom: continuity confirmed, resistance: 0 Ohm

- Front of chassis frame to earth point: continuity confirmed, resistance: 0 Ohm

|

|

645

|

Tue Sep 16 12:18:09 2025 |

Liu | Update | Interferometer Simulations | Grid search optimization for single-ring FROSTI |

| Grid search optimization for single-ring FROSTI |

| Attachment 1: Update.pdf

|

|

|

187

|

Tue Aug 1 16:22:35 2023 |

Celeste | Update | TCS | Graphical Updates to HOM RH Modification, Tuesday 8/1 |

| Slides 20-33 are newly added (data/graphs from parameter sweep feature-1/8th heater unit length varied from 10% of original to 100% of original). |

| Attachment 1: HOM_RH_Simulation_Progress_80123.pdf

|

|

|

180

|

Fri Jul 28 17:45:45 2023 |

Celeste | Update | TCS | Graphical Updates to HOM RH Modification, Friday 7/28 |

| Updated 1/8th Heater simulation modification graphs. Slides 7, 10, 16-19 are new additions. |

| Attachment 1: HOM_RH_Simulation_Progress.pdf

|

|

|

173

|

Thu Jul 27 10:18:43 2023 |

Celeste | Update | TCS | Graphical Updates to HOM RH Modification |

| Attached are updated graphs of the irradiance distribution from the 1/8th ring heater units (extruded and reduced in length). |

| Attachment 1: HOM_RH_1_8_Unit_Modification_Graphs.pdf

|

|

|

158

|

Sun Jul 16 15:21:56 2023 |

Pamella | Update | General | General update about some problems in the lab. |

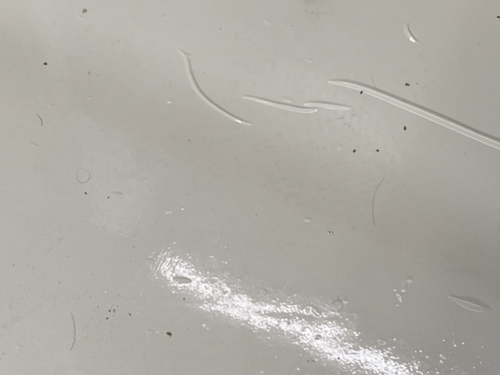

[Pamella]

General information about the lab facility.

- Changed sticky floor mats, because close to entrance the cleanroom, both sticky floor had a many died ants on top.

- The light on top of the internet cable bridge is burned out.. I just saw this today but I am not sure if was like this before.

- The ant bait traps seem very efficient and right now only a few ants are running around in the lab, most are dead in the bait traps, so probably in a day or two we can change those bait traps.

|

| Attachment 1: IMG_8637.jpg

|

|

| Attachment 2: IMG_8633.jpg

|

|

| Attachment 3: IMG_8631.jpg

|

|

|

331

|

Tue Feb 20 11:31:49 2024 |

Tyler | Update | Cleanroom | Garment Cabinet Door Replacement |

| [Luis, Luke, Pooyan, Tyler]

The replacement door for the HEPA garment cabinet arrived last week, and was installed on Thursday. However, it looks like there's a small gap between the door and where the hinge is attached to the cabinet frame. No screws were provided with the replacement door. If we want to perform any adjustments, we have to be very careful; the screws break very easily.

|

| Attachment 1: image_67190529.JPG

|

|

| Attachment 2: image_67177473.JPG

|

|

|

706

|

Thu Apr 30 12:52:26 2026 |

Mary | Update | Interferometer Simulations | Full interferometer simulation |

|

| Attachment 1: Full_interferometer.pdf

|

|

|

500

|

Tue Jan 21 10:12:02 2025 |

Luke | Summary | General | Frosti toy model |

[Luke, Liu]

Over the winter break I have been working on this desmos toy model of the Frosti. There are still a few rough spots but I belive that it is a good visual representation of a 2D slice of the frosti. |

|

646

|

Tue Sep 16 12:47:29 2025 |

Xuesi Ma | Update | Interferometer Simulations | Frosti actuation impact analysis |

| Slides |

|

389

|

Fri Jun 28 10:43:13 2024 |

Xuejun | Update | Cleanroom | Frosti |

| [Xuejun, Tyler]

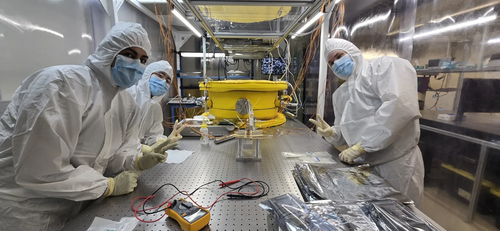

We moved Frosti into the cleanroom and debugged it to make sure everything was working. One of the DB25 pins broke off at the connector for element 1 so it needed to be recrimped. Element 6 short circuited but fixed with adjustment to the heater power pin position. We connected the power and sensor connectors to the power box and recalibrated the RTD sensors.

|

| Attachment 1: frosti.jpg

|

|

| Attachment 2: chassis.jpg

|

|

|

393

|

Fri Jul 5 13:17:44 2024 |

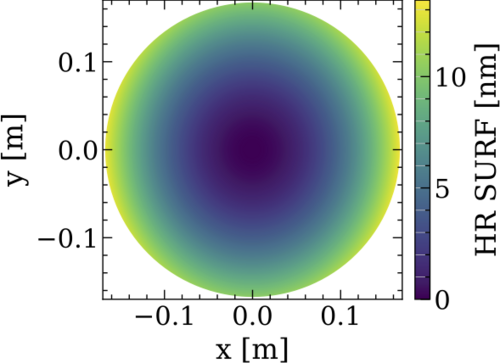

Liu | Update | Interferometer Simulations | Four-quadrant FROSTI-like RH for astigmatic thermal actuation for CE optics |

| In the CE corner layout design and down selection study, interferometer layouts with large incidence angles on some of the curved optics are being considered, such as the folding mirrors in the "long crab". This however generates astigmatic beams upon reflection and results in mode mismatches in coupled cavities that need to be mitigated. Astigmatic thermal actuation for the optics involved is thus essential. One way we are considering is to implement a FROSTI-like barrel RH that delivers different irradiance for the four quadrants. This post summarizes primitive results on the astigmatic thermal actuation for the HR surface by powering the heater elements from one diagonal differently compared to the other.

For this study, we looked at a simple case with an aLIGO-like test mass geometry (R=0.17m, H=0.2m) plus a barrel RH with 0.02m width at 0.03m from the AR surface with FEniCSx. The irradiance profiles are constant inside the width along the longitudinal direction, and zero outside the width. For the baseline non-astigmatic actuation with constant irradiance azimuthally. We have obtained roughly equal quadratic actuations along the x and y directions, as shown in figure. The total delivered power on the entire barrel is normalized to 1 W. The actuation on the curvature per power Delta S/Delta P in this non-astigmatic case thus is 0.835 uD/W.

For the astigmatic case however, the irradiance for the regions from one diagonal is increased by a given amount, compared to the non-astigmatic case, whereas for the other diagonal regions is decreased by the same amount (thus the total power is unchanged at 1 W). The HR deformation when the power is changed by 50%, for instance, is shown in picture, where the deformation along the x direction is larger than the y direction. The deformation in each direction however remains quadratic, with different curvature per powers for the x and y components, as shown in plot. The actuation on the curvature per power for an increasing amount of astigmatism is shown in plot. In terms of Zernike polynomials, the maximum amount of Z22 (astigmatism) for 1 W of total power is 2um while the remaining curvature content (Z20) is 6nm. This is shown in plot. |

| Attachment 1: SURF_05.png

|

|

| Attachment 2: SURF_xy.pdf

|

|

| Attachment 3: SURF_dsdp_converge.pdf

|

|

| Attachment 4: SURF_dsdp_astigs.pdf

|

|

| Attachment 5: overlaps_zers.pdf

|

|

| Attachment 6: SURF_xy_nonastig.pdf

|

|

| Attachment 7: SURF_xy_nonastig.pdf

|

|

|

556

|

Mon Apr 21 16:56:42 2025 |

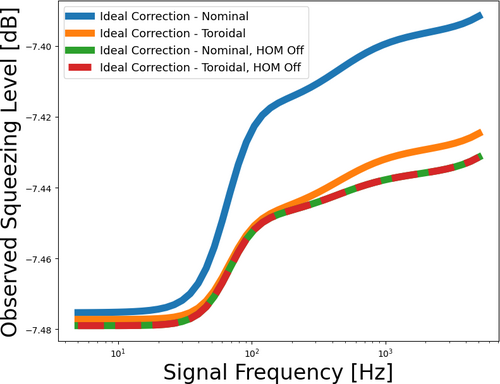

Michael | Update | Interferometer Simulations | Fixed Observed Squeezing Curve for Toroidal Mirror Case |

| We've resolved the issue with the observed squeezing curve for the toroidal mirror case showing worse performance at lower frequencies and better performance at higher frequencies compared to the nominal case. This issue was caused by the beam parameter at the squeezer being fixed before changing the radii of curvature of the mirrors. This has been changed to be fixed after changing the mirrors, and we see an improvement in the toroidal mirror case. |

| Attachment 1: updated_observed_squeezing_plot.png

|

|

|

90

|

Tue May 2 17:03:14 2023 |

Jon, Cao | Physics | VAC | First pump-down test of vacuum chamber |

[Jon, Cao]

1. Re-routing of cables

We re-routed the connections between the turbo pump and its fan to the controller. Instead of going through the side of the server rack, they are now routed along the the cable tray and came down from the top of the server rack.

2. Planning for vacuum assembly re-configuration

While preparing for our first pump-down, we notices that RGA pump line gate valve, at its fully closed position, is higher than the height of the chamber lid. The full range gauge attached to the RGA line, while not that high, can also cause obstruction during removal/ installation of the vacuum lid. The calibrated leak, eventhough is now running within the perimeter of the optical table, it stills introduce weak points that are susceptible to damage if personnel installing chamber lid may lean onto it. Thus we made a few suggested modification to the vacuum chamber assembly:

- Move the entire RGA arm to the mirrored CF port, where the Up-to-Air valve is at

- Move the Up-to-Air valve to the calibrated leak port

- Move the calibrated Ar leak the main chamber full-range gauge port

- Move the full-range gauge to the RGA line port

3. First test pump-down

- With all valves closed, we started scroll pump, pump line quickly got down to 6.08 mbar from atmospheric 1000 mbar (measured by Pirani gauge, channel 3 on controller )

- We open Lesker angled valve and let the RGA arm pumped down, Pirani gauge read 6.3 mbar while the full-range guage on RGA line reads 4.9 mbar ( channel 1 on controller )

- We open the pump line gate to expose the pump to the main volume, all gaugues readout immediate rise back up 1000 mbar. After 3 minutes, we started to see channel 3 slowly dropped down. A minute later channel 1 and 2 (main body) also dropped down. The slow pressure dropping speed and 6.3 mbar measured earlier got us suspected that there is some large leaks

- We proceed to tighten all the ports as the vacuum is pumped down. In particular, we found that large feedthrough port still required a lot of tightening up

- As we tighten up all the ports, after 40 minutes, the gauges are now

- Channel 1 : RGA line full-range gauge: 2.55E-1 mbar

- Channel 2 : Main chamber full-range gauge: 2.60E-1 mbar

- Channel 3 : Pump line Pirani gauge: 2.94E-1 mbar

Compare this to the scroll pump manual , Table 1, page 3, the ultimate pressure of the scroll pump is 2.5E-1 Torr (3.3E-1 mbar), we thus managed to achieve scroll pump ultimate pressure

- Turn on turbo pump : Change turbo pump controller from REMOTE to FRONT PANEL mode by pressing both "COUNTERS" and "MEASURE" buttons at the same time, select "MODE=FRONT"

- Shorting interlock pin: since we do not have an interlock signal for the controller, use the provided DB-9 connector that has pin 3 and 8 shorted and connect this to the P1 IN connection at the rear of the controller (see attachment 1 )

- Press "START" on the controller to start the turbo pump

- The pressure readout from the gauges quickly dropped down. After 3 minutes, the Pirani range is maxed out at 0.5E-3 mbar. After 20 minutes, we recorded the following values:

- Channel 1 : RGA line full-range gauge: 1.50E-5 mbar

- Channel 2 : Main chamber full-range gauge: 1.89E-5 mbar

- Channel 3 : Pump line Pirani gauge: 5.0E-4 mbar

This is Medium vacuum , we want to further reduce this by 2 orders of magnitude. However, we can run RGA test + helium leak test at this pressure

- Turn off turbo pump, wait for 10 minutes, turn off scroll pump, open Up-to-Air valve, all pressure gauges indicated pressure returned back to atmospheric pressure

3. To-do actions

- Run RGA test to get information about contamination status of vacuum

- Implement suggested changes in section 2

- Check and modify suspected poor connection: Pirani gauge on pump line. A gap can be seen between connection. There's no good way to tighten it with the screw. Maybe use threaded pin + hex bolt?

- Controller communications

|

| Attachment 1: PXL_20230502_203343616.jpg

|

|

| Attachment 2: PXL_20230502_210234897.MP.jpg

|

|

|

554

|

Tue Apr 15 11:37:17 2025 |

Cynthia | Update | Interferometer Simulations | Finishing up mirror coating map step |

|

| Attachment 1: updates_4_15_2025.pdf

|

|

|

181

|

Fri Jul 28 18:03:07 2023 |

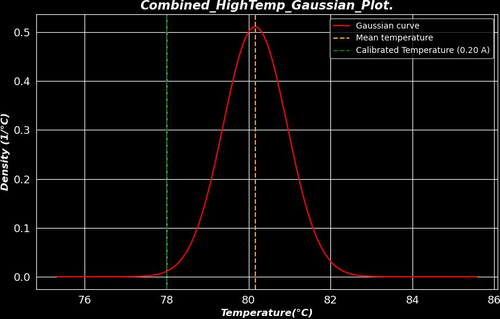

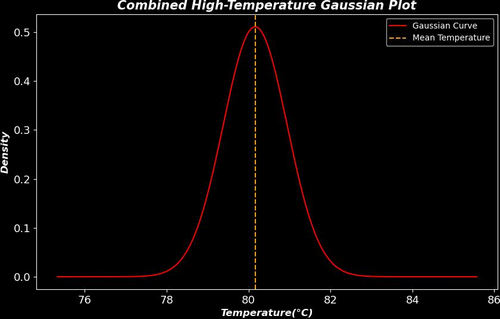

Pamella | Update | FLIR | Final plot - FLIR |

[Pamella]

- I was able to plot the final result with the data to the heater. I attached below the "3Combined_HighTemp_Gaussian_Plot." in this plot we can see better behavior on the Gaussian compared to the plot in ELOG 169, I was using the same data but with a different approach. On the ELOG 169, we have the center point isolated data and this new plot is the temperature more than 70 C isolated because we have a very good heater temperature distinguish do background. For the all data I got I was using a power current of 0.20A. To get the data I waited for 30 minutes until the heater became stable and after that, I started to take snaps, I took more than one snap for each one different 6 positions on the screen, and We can see the positions on ELOG 167.

- Also I attached the calibration plot ("calibration_plot") between the measurements with the FLIR camera and thermocouple and we can see looks good if we compare the final plot.

- For better analyses I attached a plot of the calibration line on the Gaussian plot.

- To do: I will finish the final report.

|

| Attachment 1: 29Combined_HighTemp_Gaussian_Plot.jpg

|

|

| Attachment 2: 3Combined_HighTemp_Gaussian_Plot.jpg

|

|

| Attachment 3: calibration_plot(2).png

|

.png.png)

|

|

516

|

Tue Feb 18 10:12:39 2025 |

Tyler | Update | TCS | Final RIN Plot Update |

Below is a preview of the final RIN figure that will be included in the FROSTI instrument paper. A quick summary of what is shown below:

The original RIN CSD measurement is shown on the top panel in red. Frequency bins that exhibit external electronics noise (ex. ADC, photodetector noise, etc.) are identified and shaded in gray. These noisy bins are then excluded from the dataset before beginning the next step in the analysis process: rebinning. Here, the resolution of the spectrum can be changed by averaging frequency bins together within a specified interval, with the goal of pushing the measurement curve closer to the A+ requirement shown in the figure. For demonstration below, the spectrum goes from a resolution of ~0.93 Hz to 14.90 Hz.

|

| Attachment 1: Preliminary_RIN_plot.pdf

|

|

| Attachment 2: FROSTI_ON.pdf

|

|

| Attachment 3: Dark_Noise.pdf

|

|

| Attachment 4: ADC_Noise.pdf

|

|

|

460

|

Wed Oct 16 14:13:31 2024 |

Liu | Update | | FROSTI with non uniform absorption scattering sources |

| Slides |

|

649

|

Tue Sep 30 12:26:15 2025 |

Liu | Update | Interferometer Simulations | FROSTI optimization for A# |

|

| Attachment 1: Update.pdf

|

|

|

347

|

Wed Mar 6 09:57:52 2024 |

Tyler | Update | TCS | FROSTI Wiring |

Upon finishing the FROSTI assembly last week, we ran into some electrical issues. An electrical short was found between two of the d-sub pins (2 and 8). It appears that the pins were somehow coming into contact with the aluminum surrounding them. This was causing the power supply to trip. The issue was seemingly fixed by adjusting the positioning of the cabling leading out of the reflector. When handling the device in the future, please make sure to keep the wiring as undisturbed as possible. The setup is rather fragile, and moving the cabling around could potentially reintroduce a short like this. |

|

601

|

Tue Jul 1 11:04:00 2025 |

Christina | Update | TCS | FROSTI Reconstruction II |

[Ma, Tyler, Christina]

Finished external reconstruction of the FROSTI by installing all the pins to the 2 DB 25 connectors. To ensure everything was operating correctly, we did electrical testing by testing continuity and by checking each of the heater elements' RTD and power resistance values and comparing them to what was tabulated in January. Additionally, we organized the wires and added the stands. |

| Attachment 1: IMG_4042.png

|

|